320+fpga基于EDA技术的数字频率计VHDL(300元)

- 模板:¥300.00

- 成品编号:dyy320

- 使用技术:FPGA

- 数据库:无

- 最后更新:2018-09-17 16:29

注意:QQ1764030875,qq1834660615为本网站唯一成品的账号,其他均为盗版

计算机毕业设计源码网:我们提供的源码通过邮箱或者QQ传送,如果有啥问题直接联系客服

素材描述:

本套fpga设计包含程序,原理图,演示视频

本套设计要实现的功能如下:

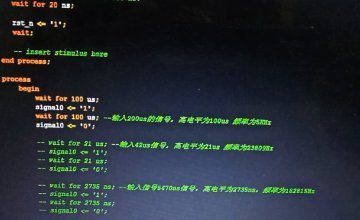

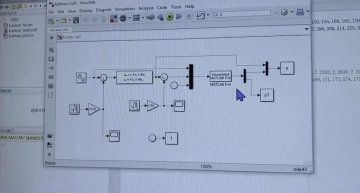

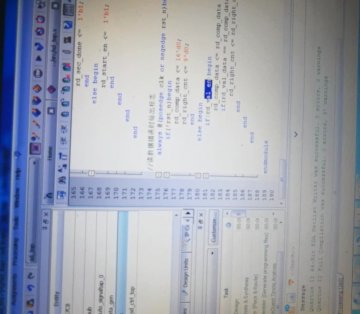

本设计要求分析数字频率计的功能,完成功能模块的划分,分别用VHDL语言完成底层模块的设计和以原理图的方法完成顶层模块的设计,分别对各个模块以及顶层模块进行仿真分析,最后在硬件开发平台上进行测试。

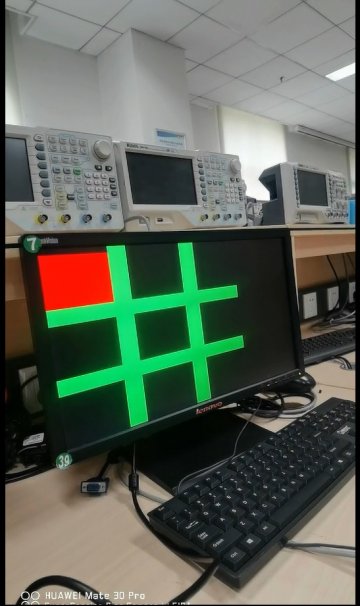

1. 本设计可以实现4个十进制数字显示的数字式频率计,其测量范围为10MHz,为了提高测量精度,量程分别为10kHz,100kHz,1MHz,10MHz 4档,即最大读数分别为9.99kHz,99.9kHz,999kHz,9999kHz,能自动换挡。 FPGA进行相位差测量运算并送显示电路显示,测相绝对误差不大于±0.5;

2.在QuartusII中完成功能仿真和时序仿真。

本设计要求分析数字频率计的功能,完成功能模块的划分,分别用VHDL语言完成底层模块的设计和以原理图的方法完成顶层模块的设计,分别对各个模块以及顶层模块进行仿真分析,最后在硬件开发平台上进行测试。

1. 本设计可以实现4个十进制数字显示的数字式频率计,其测量范围为10MHz,为了提高测量精度,量程分别为10kHz,100kHz,1MHz,10MHz 4档,即最大读数分别为9.99kHz,99.9kHz,999kHz,9999kHz,能自动换挡。 FPGA进行相位差测量运算并送显示电路显示,测相绝对误差不大于±0.5;

2.在QuartusII中完成功能仿真和时序仿真。

标签

全部评论 / 0